- 您现在的位置:买卖IC网 > Sheet目录329 > IDT70V5388S166BGI (IDT, Integrated Device Technology Inc)IC SRAM 1.125MBIT 166MHZ 272BGA

IDT70V5388/78

3.3V 64/32K x 18 Synchronous FourPort? Static RAM

Industrial and Commercial Temperature Ranges

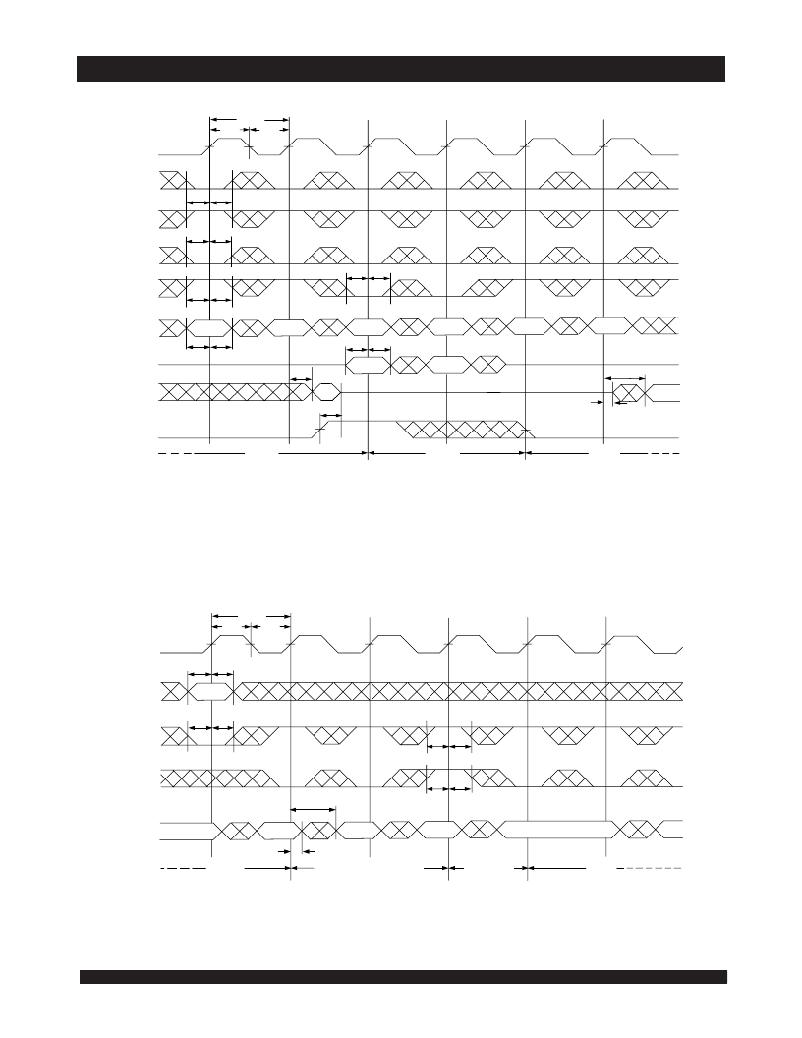

Timing Waveform of Read-to-Write-to-Read ( OE Controlled) (2)

t CYC2

CLK

CE 0

t CH2

t CL2

CE 1

t SC

t SB

t HC

t HB

LB , UB

t SW t HW

R/ W

t SW t HW

(3)

ADDRESS

An

An +1

An + 2

An + 3

An + 4

An + 5

t SA

t HA

t SD

t HD

DATA IN

DATA OUT

(1)

t CD2

Qn

t OHZ

(4)

Dn + 2

Dn + 3

t CKLZ

t CD2

Qn + 4

OE

READ

WRITE

READ

5649 drw 12

,

NOTES:

1. Output state (High, Low, or High-impedance) is determined by the previous cycle control signals.

2. CNTLD = V IL ; CNTINC , CNTRST , MRST , MKLD , MKRD and CNTRD = V IH .

3. Addresses do not have to be accessed sequentially since CNTLD = V IL constantly loads the address on the rising edge of the CLK;

numbers are for reference use only.

4. This timing does not meet requirements for fastest speed grade. This waveform indicates how logically it could be done if timing so allows.

Timing Waveform of Read with Address Counter Advance (1)

t CYC2

CLK

t CH2

t CL2

t SA

t HA

ADDRESS

An

t SCLD t HCLD

CNTLD

t SCLD t HCLD

CNTINC

t CD2

t SCLD t HCLD

DATA OUT

Qx - 1 (2)

Qx

Qn

Qn + 1

Qn + 2 (2)

Qn + 3

,

t DC

NOTES:

READ

EXTERNAL

ADDRESS

READ WITH COUNTER

COUNTER

HOLD

READ

WITH

COUNTER

5649 drw 13

1. CE 0 , LB and UB = V IL ; CE 1 , CNTRST , MRST , MKLD , MKRD and CNTRD = V IH .

2. If there is no address change via CNTLD = V IL (loading a new address) or CNTINC = V IL (advancing the address), i.e. CNTLD = V IH and CNTINC = V IH , then

the data output remains constant for subsequent clocks.

16

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT70V631S10PRFG

IC SRAM 4MBIT 10NS 128TQFP

IDT70V639S12PRFI

IC SRAM 2.25MBIT 12NS 128TQFP

IDT70V659S12DRI

IC SRAM 4MBIT 12NS 208QFP

IDT70V7319S166BCI

IC SRAM 4MBIT 166MHZ 256BGA

IDT70V7339S166BCI

IC SRAM 9MBIT 166MHZ 256BGA

IDT70V7519S166DRI

IC SRAM 9MBIT 166MHZ 208QFP

IDT70V7599S133DRI

IC SRAM 4MBIT 133MHZ 208QFP

IDT70V9089L6PF

IC SRAM 512KBIT 6NS 100TQFP

相关代理商/技术参数

IDT70V5388S166BGI8

功能描述:IC SRAM 1.125MBIT 166MHZ 272BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR)

IDT70V5388S200BC

功能描述:IC SRAM 1.125MBIT 200MHZ 256BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR)

IDT70V5388S200BC8

功能描述:IC SRAM 1.125MBIT 200MHZ 256BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR)

IDT70V5388S200BCG

功能描述:IC SRAM 1.125MBIT 200MHZ 256BGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR)

IDT70V5388S200BG

功能描述:IC SRAM 1.125MBIT 200MHZ 272BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR)

IDT70V5388S200BG8

功能描述:IC SRAM 1.125MBIT 200MHZ 272BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR)

IDT70V631S10BC

功能描述:IC SRAM 4MBIT 10NS 256BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:2,500 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:1K (128 x 8) 速度:100kHz 接口:UNI/O?(单线) 电源电压:1.8 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽) 供应商设备封装:8-MSOP 包装:带卷 (TR)

IDT70V631S10BC8

功能描述:IC SRAM 4MBIT 10NS 256BGA RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR)